# BERTScope<sup>™</sup>, BERTScope<sup>™</sup>S, and BERTScope Spg Signal Integrity Instruments

## Technical Specifications

The Vision of a Scope, the Confidence of a BERT, and Clock Recovery you can Count on.

### **Benefits:**

- Integrated Signal Integrity Analyzer using the same acquisition circuitry for time, error and jitter domain measurements, to give "same observer" measurements that tie together for faster troubleshooting of your problem devices

- Unique analysis toolkit gives you unrivaled information quality and depth

- 12.5 Gb/s and 7.5 Gb/s (upgradeable) models will cover your needs as your application bit rates increase

### **Applications:**

- Serial Bus Design

- Semiconductor IC Evaluation

- Jitter Tolerance Compliance Testing

- High Speed Backplane Design

- Optical Transceiver Design and Manufacturing

- Recirculating Fiber Loop Experiments

# BERTScope, BERTScope S, and BERTScope Spg Technical Specifications

### Contents

| Pattern Generator:         Data and Clock Outputs         Ancillary Interfaces         Clock Path Details         Stressed Eye Option                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Error Detector:         Data and Clock Inputs         Ancillary Interfaces         Rear Panel Interface         User Interfaces         Lye Diagram Capabilities         Physical Layer Test Data Options         Litter Tolerance Option |

| General Specifications15                                                                                                                                                                                                                  |

| Ordering Information16                                                                                                                                                                                                                    |

| Model                                                            | Applicable Pages                                                                   |

|------------------------------------------------------------------|------------------------------------------------------------------------------------|

| BERTScope 12500A, 7500A<br>Signal Integrity Analyzer             | Pattern Generator: 3, 4<br>Error Detector: 7 - 12, 14<br>General: 15, 16           |

| BERTScope 12500B, 7500B<br>Signal Integrity Analyzer with Stress | All                                                                                |

| BERTScope Spg 12500B<br>Stress Pattern Generator                 | Pattern Generator: 3 - 6<br>Error Detector: 10 (user interface)<br>General: 15, 16 |

## **Pattern Generator**

Input/ Output Specifications

CLOCK

OUTPUT

PATTERN

GENERATOR

DATA

OUTPUT

# BERTScope<sup>\*</sup>

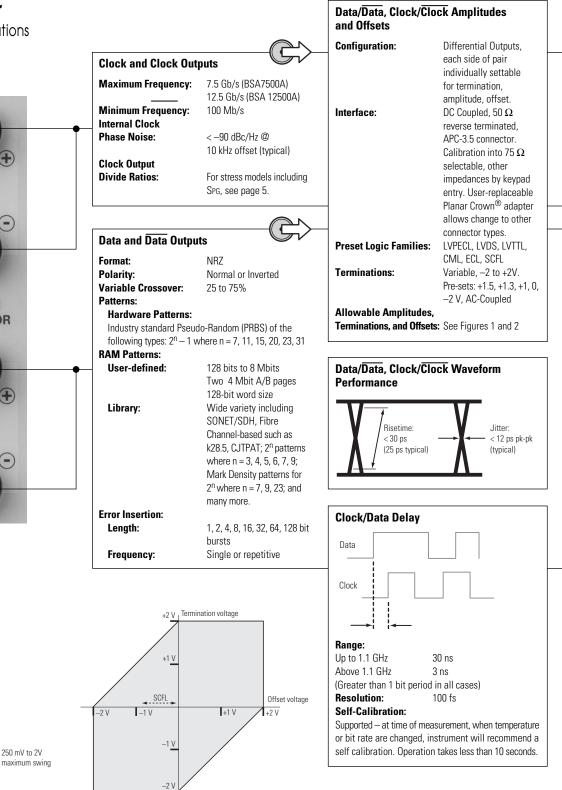

Figure 1. Amplitude range.

Figure 2. Allowable combinations of termination and offset. Amplitude swings between 0.25 and 2 V allowed; should fit inside shaded area of graph. For example, SCFL uses a 0 V termination, and operates between approximately 0 and -0.9 V; as shown with dotted arrow, it falls within the operating range.

Planar Crown<sup>®</sup> is a registered trademark of Aeroflex/Weinschel, www.aeroflex-weinschel.com

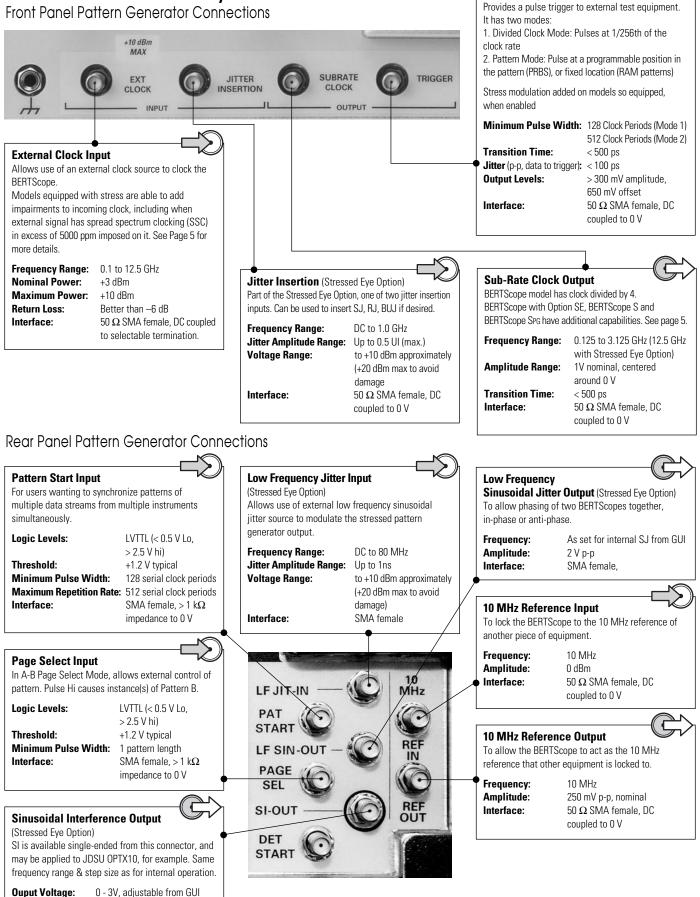

**Trigger Output**

## Pattern Generator Ancillary Connections

Interface:

50  $\Omega$  SMA female

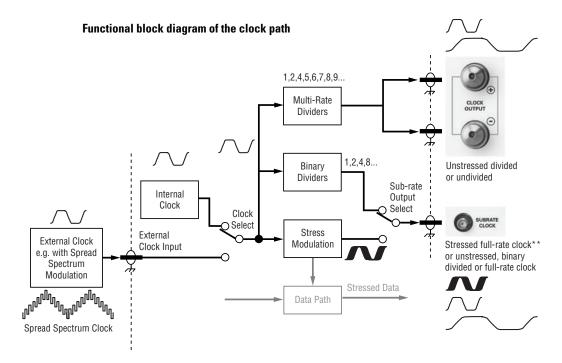

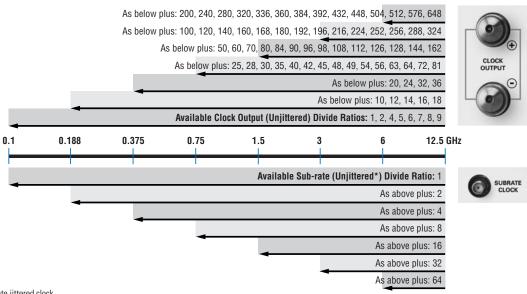

## New Clocking For Models With Stress Capability

Models with stress (BERTScope with Option SE fitted, BERTScope S, and BERTScope SPG) have a number of new capabilities to give clock flexibility. These include the ability to stress an external clock, take incoming SSC, and output a wide variety of sub-rate clocks.

#### Available divide ratios from clock-related output, by bit rate, using the internal clock<sup>†</sup>

\* This output can also provide a full-rate jittered clock.

- † All listed ratios available for an external clock input over entire bit-rate range, limitations for internal clock only.

- \*\* Stress may be added to an external clock on appropriate models. Stress operating range is from 1.45 to 11.2 Gb/s. External clock must have a duty cycle of  $50\% \pm 2\%$ .

## BERTScope

Gb/s Signal Analysis

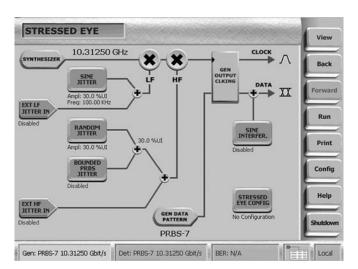

## Pattern Generator Stressed Eye

### Generator Option

- Flexible, integrated stressed eye impairment addition to the internal or an external clock

- · Easy set-up, with complexity hidden from the user with no loss of flexibility

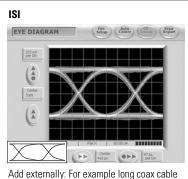

- Verify compliance to multiple standards using the BERTScope and external ISI filters. Standards such as:

- OIF CEI

- Serial-ATA II

- PCI-Express

- XFI

- · Sinusoidal interference may be inserted in phase or in anti-phase, or sent externally to a JDSU OPTX10 optical reference transmitter for the creation of 10 Gigabit Ethernet-compliant stressed eyes for receiver jitter tolerance testing

- · Sinusoidal jitter may be locked between two BERTScopes in phase or anti-phase, as required by OIF CEI

#### **Flexible External Jitter Interfaces:**

- Front Panel External High Frequency Jitter Input Connector Jitter from DC to 1.0 GHz up to 0.5 UI (max.) may be added, of any type that keeps with amplitude and frequency boundaries

- Rear Panel External SJ Low Frequency Jitter Input Connector Jitter from DC to 80 MHz up to 1ns (max) may be added

- · Rear Panel SJ Output

- Sinusoidal Interference Output rear panel connector

### **Amplitude & ISI Impairments**

length, or Bessel-Thompson 4th Order Filter with -3 dB point at 0.75 of Bit Rate etc.

For applications requiring circuit board dispersion, the BERTScope differential ISI accessory may be used.

#### Sinusoidal Interference

- 100 MHz to 2.5 GHz

- Adjustable in 100 kHz steps

- Adjustable from 0 to 400 mV

- Common mode or differential

- Available from rear panel 50 Ω SMA connector, single-ended with data amplitude from 0 to 3 V adjustable from GUI, same frequency range and step size as internal adjustment

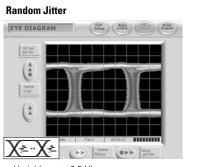

### **Jitter Impairments**

## **Bounded Uncorrelated Jitter** EYE DIAGRAM Eye (1 ▓⊣▓≩ Center OFF (6 ps

- Internal PRBS Generator PN-7

- Variable up to 0.5 UI

- 100 Mb/s to 2.0 Gb/s

- · Band limited by selected filters see table below:

| BUJ Rate       | Filter (MHz) |

|----------------|--------------|

| 100 to 499     | 25           |

| 500 to 999     | 50           |

| 1,000 to 1,999 | 100          |

| 2,000          | 200          |

#### Sinusoidal Jitter

Notes: Specified for data rates from 1.45 Gb/s to 11.2 Gb/s. Usable with limited performance to 622 Mb/s.

Internal RJ, BUJ, and external high frequency jitter input limited to 0.5 UI, combined.

Rear panel low frequency jitter input can be used to impose additional jitter; SJ and external jitter sum total cannot exceed jitter magnitude limits given for SJ below.

- · Variable up to 0.5 UI

- Band limited 10 MHz to 1 GHz

- Crest factor of 16 (Gaussian to at least 8

- standard deviation or  $\sim 1 \times 10^{-16}$  probability)

| Data Rate    | Internal SJ Frequency<br>Range |                     |  |

|--------------|--------------------------------|---------------------|--|

|              | 1kHz to<br>10 MHz              | 10 MHz to<br>80 MHz |  |

| 10.3125 Gb/s | 10.3 UI                        | 2.1 UI              |  |

| 9.9545 Gb/s  | 10.0 UI                        | 2.0 UI              |  |

| 8.5 Gb/s     | 8.5 UI                         | 1.7 UI              |  |

| 6.25 Gb/s    | 6.3 UI                         | 1.3 UI              |  |

| 6 Gb/s       | 6.0 UI                         | 1.2 UI              |  |

| 5 Gb/s       | 5.0 UI                         | 1.0 UI              |  |

| 4.25 Gb/s    | 4.3 UI                         | 0.9 UI              |  |

| 3.125 Gb/s   | 3.1 UI                         | 0.6 UI              |  |

| 3 Gb/s       | 3.0 UI                         | 0.6 UI              |  |

| 2.5 Gb/s     | 2.5 UI                         | 0.5 UI              |  |

| 2.4883 Gb/s  | 2.5 UI                         | 0.5 UI              |  |

| 2.125 Gb/s   | 2.1 UI                         | 0.4 UI              |  |

| 1.5 Gb/s     | 1.5 UI                         | 0.3 UI              |  |

# BERTScope

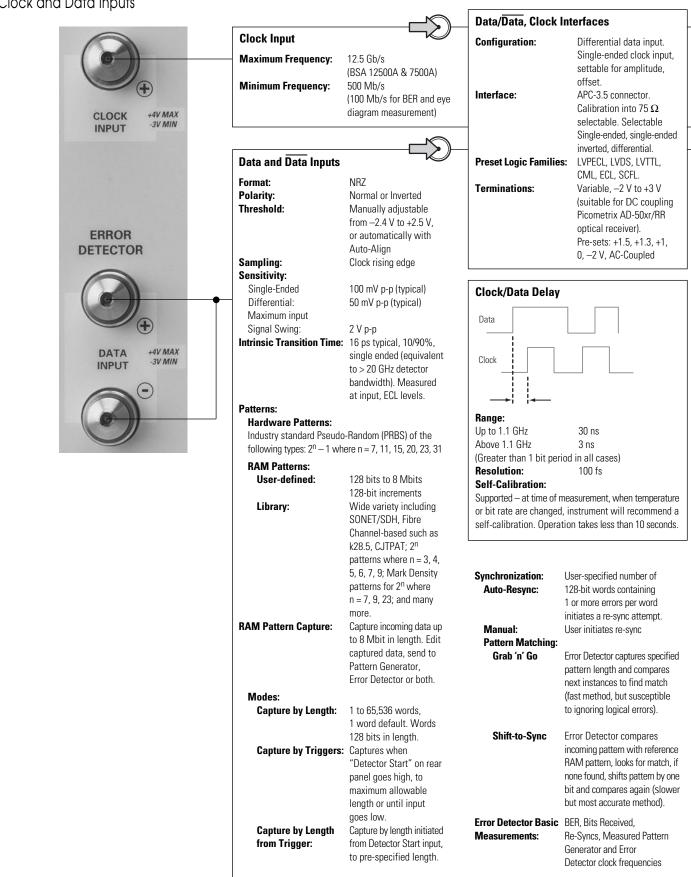

**Error Detector**

Clock and Data Inputs

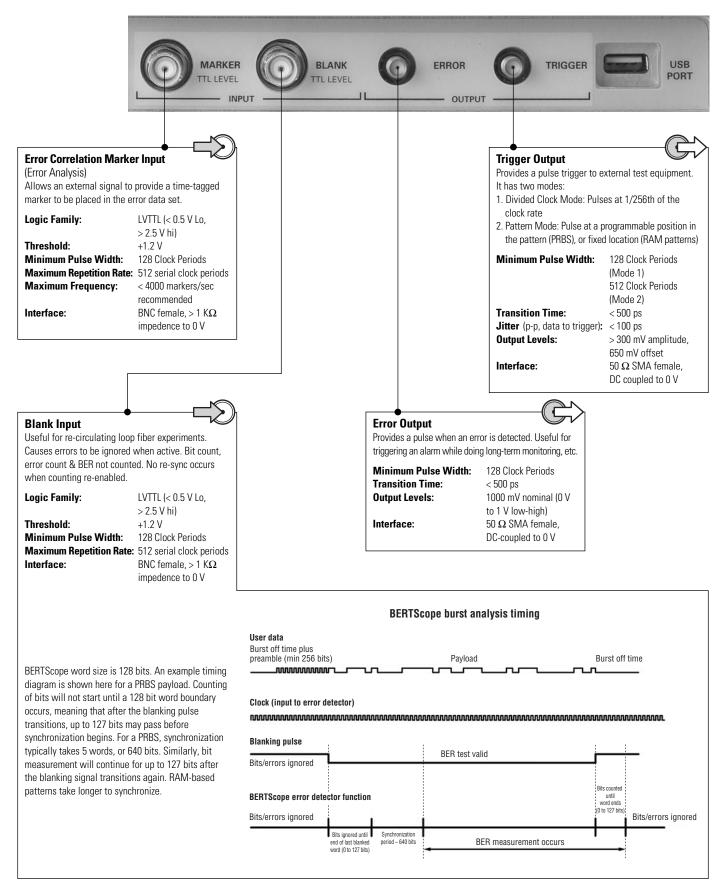

## **Error Detector Ancillary Connections**

Front Panel Error Detector Connections

### BERTScope" 12.5 Gb/s Signal Analysis

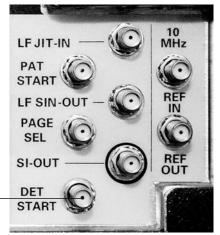

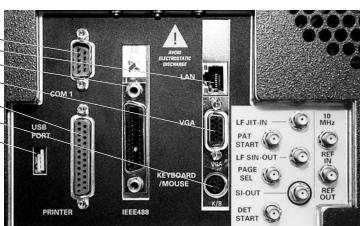

## Rear Panel Error Detector Connections

| Detector Start Input<br>Used to trigger the acquisitio<br>the Error Detector reference<br>level starts capture. | 8                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amplitude:<br>Threshold:<br>Minimum Pulse Width:<br>Maximum Repetition Rate:<br>Interface:                      | $ \begin{array}{l} \text{LVTTL (< 0.5 V Lo,} \\ > 2.5 V \text{ hi}) \\ +1.2 V \\ 128 \text{ serial clock periods} \\ 512 \text{ serial clock periods} \\ \text{SMA female, > 1k} \\ \text{impedance to 0 V} \end{array} $ |

| (Not present for BE                                                                                             | RTScope Spg)                                                                                                                                                                                                              |

#### BERTScope" 12.5 Gb/s Signal Analysis

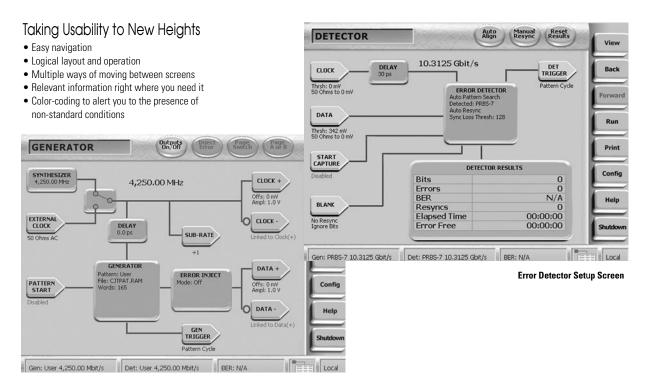

## **User Interfaces**

Pattern Generator Set-Up Screen

|                                                                                                              | R<br>n - D:\BitAløzer\                                                                                        | UserPatter                                                                             | le Edit Send Option                                                                                           |                           |                                                             |               |                    |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------|---------------|--------------------|

| % Imported R<br>ASSIGN WIDTH<br>%<br>0x3eaa2aaaa<br>0xa6a5a987<br>0x71e3871e                                 | AM file<br>32<br>0xaa3eaa2a<br>0x3eaa2aaa<br>0x1e3871e3<br>0x3871e387                                         | 0xaaaa<br>0xaa3e;<br>0x871e:<br>0x1e387                                                | New<br>Open<br>Save                                                                                           | Enter D                   | etector RAM                                                 |               | Length:<br>words 💌 |

| 0xe3871e38<br>0x871e3871<br>0x1e3871e3<br>0x3871e387<br>0x71e3871e<br>0xe3871e38<br>0x871e3871<br>0x1e3871e3 | 0x71e3871e<br>0xe3871e38<br>0x871e3871<br>0x1e3871e3<br>0x3871e387<br>0x71e3871e<br>0xe3871e387<br>0x871e3871 | 0x38714<br>0x71e38<br>0xe3871e3<br>0x871e3<br>0x1e387<br>0x38714<br>0x71e38<br>0xe3871 | Save As<br>Close<br>Print                                                                                     | 7                         | 8                                                           | 9<br>6        | DEL                |

| 0×3871e387<br>0×71e3871e<br>0×e3871e38<br>0×871e3870<br>0×aaaaaaaa<br>0×aaaaaaaa<br>0×aaaaaaaa               | 0x1e3871e3<br>0x3871e387<br>0x71e3871e<br>0xbc78f4aa<br>0xaaaaaaaa<br>0xaaaaaaaa<br>0xaaaaaaaaa               | 0x871e3<br>0x1e387<br>0x3871e<br>0xaaaaa<br>0xaaaaa<br>0xaaaaa<br>0xaaaaa              | Check Syntax                                                                                                  | 1                         | 2                                                           | 3             | :                  |

| 0xaaaaaaaa<br>0xab9c9686<br>0xaa2aaaaa<br>0x2aaaaa3e                                                         | Oxaaaaaaaa<br>Oxe6c16aaa<br>Ox3eaa2aaa<br>Oxaa2aaaaa                                                          | 0x5555e<br>0x9aa63<br>0xaa3ee<br>0x3eaae<br>5 words                                    | Capture by Length<br>Capture by Triggers<br>Capture by Length when Triggered<br>7 10.3123 GBT(3) BER 0.006400 | Detector RA<br>words. The | efines how mu<br>M. The range<br>word size is 12<br>Default | is 1 words to |                    |

## Editor Screen

- Used for pattern editing of standard and AB Page Select patterns, also mask editing

- Views in Binary, Decimal or Hexadecimal

- Support for variable assignments, repeat loops, seeding of PRBS patterns

- Capture and editing of incoming data for example, to make a repeating pattern out of real-world traffic

- Capture is available by trigger, by length or by length following a trigger

- Capture is by number or words, 1 word is 128 bits. For example, a PRBS-7 (127 bits long) would be captured as 127 words, and would have overall length of 16,256 bits.

### BERTScope Built-In Parametric **Measurements**

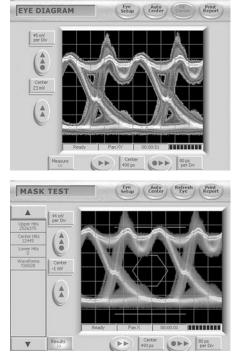

All BERTScopes come with Eye Diagrams and Mask Test capabilities as standard, along with Error Analysis.

### Eye Diagram

- 280x350 pixel waveform display

- Deep acquisition

- Automatic Measurements include:

- Rise Time

- Fall Time

- Unit Interval (Data, and also Clock)

- · Eye Amplitude

- Noise Level of 1 or 0

- Eye Width

- Eye Height

- Eye Jitter (p-p and RMS)

- 0 Level, 1 Level

- Extinction Ratio

- Vertical Eye Closure Penalty (VECP)

- Dark Calibration

- Signal-to-Noise Ratio

- Vp-p, Vmax, Vmin, Crossing Levels

- Rising and Falling Crossing Level (picoseconds)

- Overshoot 0 level and 1 level

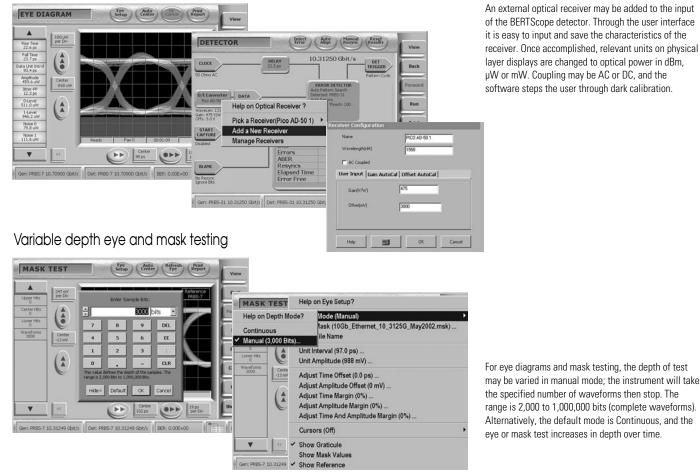

## Mask Testing

- Library of standard masks e.g. XFP, or edit custom masks

- Addition of positive or negative mask margin

- Import of measured BER Contour to become process control mask

- At least 1000x the sample depth of traditional sampling oscilloscope masks is ideal for ensuring the absence of rare event phenomena

## **Optical units**

For eye diagrams and mask testing, the depth of test may be varied in manual mode; the instrument will take the specified number of waveforms then stop. The range is 2,000 to 1,000,000 bits (complete waveforms). Alternatively, the default mode is Continuous, and the eye or mask test increases in depth over time.

## **Physical Layer Test Option**

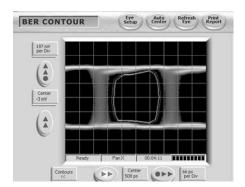

### **BER Contour Testing**

- Executed with same acquisition circuitry as Eye Diagram measurements for maximum correlation

- As-needed delay-calibration for accurate points

- Automatic scaling, one button measurement

- Extrapolates contours from measured data, increasing measurement depth with run-time and repeatedly updating curve-fits

- Easy export of fitted data in CSV format

- Contours available from 10<sup>-6</sup> to 10<sup>-16</sup> in decade steps

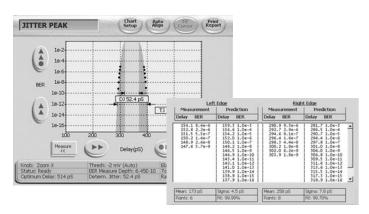

### Jitter Measurements

- Testing to T11.2 MJSQ BERTScan methodology (also called 'Bathtub Jitter')

- Deep measurements for quick and accurate extrapolation of Total Jitter at user-specified level, or direct measurement

- Separation of Random and Deterministic components, as defined in MJSQ

- As-needed delay-calibration for accurate points

- Easy export of points in CSV format

- Easy one-button measurement

- · User-specified amplitude threshold level, or automatic selection

- Selectable starting BER to increase accuracy when using long patterns, as defined in MJSQ

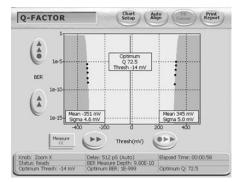

### Q Factor Measurement

- One-button measurement of a vertical cross-section through the middle of the eye

- Easy visualization of system noise effects

- Export of data in CSV format

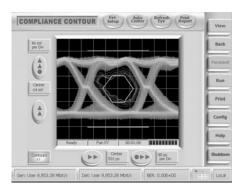

### Compliance Contour

- Validation of transmitter eye performance to standards such as XFP/XFI and OIF CEI

- Overlay compliance masks onto measured BER contours and easily see whether devices pass the BER performance level specified

## Live Data Analysis Option

The live data option is designed to measure parametric performance of traffic that is either unknown or non-repeating. This can include traffic with idle bits inserted such as in systems with clock rate matching. It is also suitable for probing line cards, etc.

The option uses one of the two front-end decision circuits to decide whether each bit is a one or zero by placing it in the center of the eye. The other is then used to probe the periphery of the eye to judge parametric performance. This method is powerful for physical layer problems, but will not identify logical problems due to protocol issues, where a zero was sent when it was intended to be a one.

Live data measurements can be made using BER Contour, Jitter Peak, Q Factor. Eye diagram measurements can be made on live data without the use of this option, providing a synchronous clock is available.

The Live Data Analysis option requires the Physical Layer Test Option.

## BERTScope

12.5 Gb/s Signal Analysis

28.032.399.008

PRBS-15

0.00.15

OFF

RER: No Svo

....

101000111100100010

Chart Auto FR Setup Center Cursor

Play from File ...

Back

Back

BASIC BE

STRIP CHART

10

18-

Durst Put

Det: No Clock

10.312.54 Mbit Det: PRBS-7 10.312.54 Mbit/s EER: 2.13E-0

\*\*

PATTERN SENSITIVITY

178

-----

4

(

.

Total Bits Total Errors

Non-Burst Related Total Bit Error Rate (BER) Burst Related Non-Burst Related Burst Events

rkers uelch Events

## Error Analysis

Error analysis is a powerful series of views that associate error occurrences so that underlying patterns can be easily seen. It is easy to focus in on a particular part of an eye diagram, move the sampling point of the BERTScope there, and then probe the pattern sensitivity occurring at that precise location. For example, it is straightforward to examine which patterns are responsible for late or early edges.

Many views come standard with the BERTScope family.

#### **Analysis Views**

- Error Statistics: A tabular display of bit and burst error counts and rates.

- Strip Chart: A strip chart graph of bit and burst error rates.

- **Burst Length:** A histogram of the number of occurrences of errors of different lengths.

- Error Free Interval: A histogram of the number of occurrences of different error free intervals.

- Correlation: A histogram showing how error locations correlate to user-set block sizes or external Marker signal inputs.

- Pattern Sensitivity: A histogram of the number of errors at each position of the bit sequence used as the test pattern.

- Block Errors: A histogram showing the number of occurrences of data intervals (of a user-set block size) with varying numbers of errors in them.

#### **Error Location Capture**

Live Analysis Error Logging Capacity Error Events/Second Maximum Burst Length Continuous Max. 2 GB file size 10,000 32 kbits

## **Error Analysis Options**

### Forward Error Correction Emulation

Because of the patented error location ability of the BERTScope, it knows exactly where each error occurs during a test. By emulating the memory blocks typical of block error correcting codes such as Reed-Solomon architectures, bit error rate data from uncorrected data channels can be passed through hypothetical error correctors to find out what a proposed FEC approach would yield. Users can set up error correction strengths, interleave depths, and erasure capabilities to match popular hardware correction architectures.

| Current Interval                                                            | TOTAL ACCUMULATION        | Processing       | -       |

|-----------------------------------------------------------------------------|---------------------------|------------------|---------|

| Current interval                                                            | TO THE PIECE PIECE        | Processing       | Back    |

| Total Accumulation                                                          | Before FEC                | After FEC        |         |

| Error Count                                                                 | 75.114                    | 18.445           | Forwar  |

| Error Rate                                                                  | 2.685-06                  | 7.026-07         | 10000   |

| Bit Count                                                                   | 28.032.398.880            | 26,273,503,264   |         |

| Data Rate                                                                   | 1,500.00 Mbit/s           | 1,405.98 Mbit/s  | Run     |

| Inner-Code Status (blocks)<br>Outer-Code Status (blocks)<br>alysis<br>ine a | 437<br>6,642<br>0         | 15,463<br>0<br>0 | Config  |

| ERROR ERROR                                                                 | ERROR ANAL<br>FILTER ANAL |                  | Help    |

| topped Example.uer<br>(175 kB)                                              | FEC Enabled Unknown       | n Pattern        | Station |

## Error Statistics View showing link performance in terms of bit and burst occurrences.

Viewing bit and burst error performance over time. This can useful while temperature cycling as part of troubleshooting, for example.

Pattern Sensitivity is a powerful way of examining whether error events are pattern related. It shows which pattern sequences are the most problematic, and operates on PRBS and user-defined patterns.

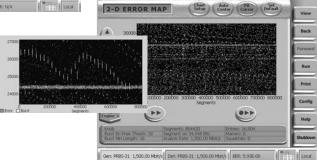

### 2-D Error Mapping

This analysis creates a two-dimensional image of error locations from errors found during the test. Error mapping based on packet size or multiplexer width can show if errors are more prone to particular locations in the packet or particular bits in the parallel bus connected to the multiplexer. This visual tool allows for human eye correlation, which can often illuminate error correlations that are otherwise very difficult to find-even with all the other error analysis techniques.

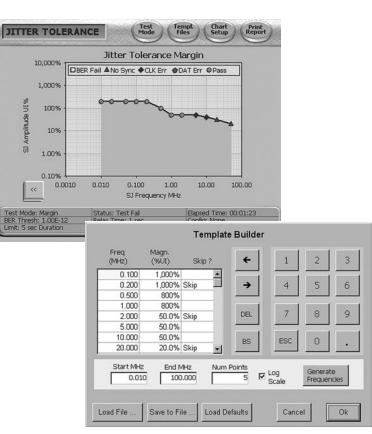

## Jitter Tolerance Template Option

Many standards call for SJ to be stepped through a template with different SJ amplitudes at particular modulation frequencies. This is easy with the built in Jitter Tolerance function which automatically steps through a template that you designed, or one of the many standard templates in the library.

This functionality is standard on BERTScope B models, and is an upgrade software option for customers who already own BERTScopes with stress. It is not available for the SPG model.

#### **Standard Library of Templates**

- 10 GBASE LX4 802.3ae 3.125Gb/s

- 10 GbE 802.3ae 10.3125Gb/s

- OIF CEI 11G Datacom Rx Ingress (D) 11Gb/s

- OIF CEI 11G Telecom Rx Egress (Re) 11Gb/s

- OIF CEI 11G Telecom Rx Ingress (Ri) 11Gb/s

- OIF CEI 11G Total Wander 11.1Gb/s

- OIF CEI 11G Total Wander 9.95Gb/s

- OIF CEI 6G Total Wander 4.976Gb/s

- OIF CEI 6G Total Wander 6.375Gb/s

- Fully Buffered DIMM 3.2Gb/s

- Fully Buffered DIMM 4.0Gb/s

- Fully Buffered DIMM 4.8Gb/s

- Fibre Channel 1.0625Gb/s

- Fibre Channel 2.125Gb/s

- Fibre Channel 4.25Gb/s

- Serial Attached SCSI 1.5Gb/s

- Serial Attached SCSI 3.0Gb/s

- XAUI 3.125Gb/s

- XFI ASIC Rx Input Datacom (D) 10.3125Gb/s

- XFI ASIC Rx Input Datacom (D) 10.519Gb/s

- XFI ASIC Rx Input Telecom (D) 10.70Gb/s

- XFI ASIC Rx Input Telecom (D) 9.95328Gb/s

- XFI Host Rx Input Datacom (C) 10.3125Gb/s

- XFI Host Rx Input Datacom (C) 10.519Gb/s

- XFI Host Rx Input Telecom (C) 10.70Gb/s

- XFI Host Rx Input Telecom (C) 9.95328Gb/s

- XFI Module Tx Input Datacom (B') 10.3125Gb/s

- XFI Module Tx Input Datacom (B') 10.519Gb/s

- XFI Module Tx Input Telecom (B') 10.515(b)/s

XFI Module Tx Input Telecom (B') 10.70Gb/s

- XFI Module TX Input Telecom (B') 9.95328Gb/s

XFI Module TX Input Telecom (B') 9.95328Gb/s

Some of the areas of adjustment include:

- BER confidence level

- Test duration per point

- BER threshold

- Test device relaxation time

- Imposition of percentage margin onto template

Test precision

Also included is the ability to test beyond the template to device failure at each chosen point, and the ability to export data either as screen images or CSV files.

# BERTScope<sup>m</sup> 12.5 Gb/s Signal Analysis

## General

## **PC-Related**:

| Display:              | TFT Touch Screen          |

|-----------------------|---------------------------|

|                       | 640 x 480 VGA             |

| Touch Sensor:         | Analog Resistive          |

| Processor:            | 1 GHz Pentium or          |

|                       | equivalent                |

| Hard Disk:            | 20 GB or greater          |

| DRAM:                 | 256 MB                    |

| Operating System:     | Windows 2000              |

| Remote Control:       | IEEE-488 (GPIB) or TCP/IP |

| Sunnorted Interfaces: |                           |

#### rted Interfaces:

| Serial (RS-232) —    |                      |

|----------------------|----------------------|

| RJ-45 Ethernet) —    | Network (100 Base-T  |

| IEEE-488 (GPIB)      |                      |

| itor (DB-15 VGA) 🔶   | Mon                  |

| r Port (Centronix) 🖯 | Printer              |

| Keyboard (Micro)     | k                    |

| Mouse (PS/2)         |                      |

| nel, 1 rear panel) 듰 | USB 1.0 (1 front par |

|                      |                      |

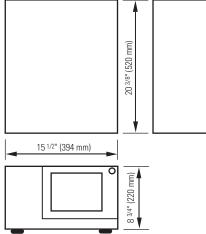

#### **Physical:**

| •                                            |                                                                                                                                                                                                              |   |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Power:<br>Voltage:<br>Weight:<br>Dimensions: | < 400 Watts<br>90 to 240 V AC, 50 to 60 Hz<br>55 lbs (25 kg)<br>8 <sup>3</sup> / <sub>4</sub> " (H) x 15 <sup>1</sup> / <sub>2</sub> " (W)<br>x 20 <sup>3</sup> / <sub>8</sub> " (D)                         |   |

| Environmental:                               |                                                                                                                                                                                                              |   |

| Warm-up time:<br>Operating                   | 20 minutes                                                                                                                                                                                                   |   |

| Temperature Range:<br>Humidity:              | 10 to 40 °C<br>Non-condensing at<br>40 °C, 15 to 95%                                                                                                                                                         |   |

| Certifications:                              | EU EMC Directive<br>(CE-Marked)<br>UL: Underwriters Labs<br>(US) certification<br>CSA (Canada)                                                                                                               |   |

| Support:<br>Period:                          | 1 year (extendable to 3 years                                                                                                                                                                                |   |

| Coverage:                                    | with orderable option)<br>Hardware repair or<br>replacement, at SyntheSys<br>Research's discretion.<br>Also covers software<br>updates. Repairs performed<br>at the Menlo Park,<br>California, USA facility. | ( |

| Calibration interval                         | 1 year                                                                                                                                                                                                       |   |

|                                              |                                                                                                                                                                                                              |   |

#### NOTES

Rise times are measured 20% to 80% unless otherwise stated. Specifications are following a 20 minute warm-up period. Specifications subject to change.

# BERTScope<sup>™</sup> 12.5 Gb/s Signal Analysis

#### www.bertscope.com

#### **BERTScope Products**

|                                                                        | BERTScope Model |                       |                           |                       |                       |

|------------------------------------------------------------------------|-----------------|-----------------------|---------------------------|-----------------------|-----------------------|

|                                                                        | 7500A           | S 7500B               | 12500A                    | S 12500B              | SPG 12500B            |

|                                                                        | Generator &     | Stress                | Generator &               | Stress                | Stress                |

|                                                                        | Analyzer        | Generator &           | Analyzer                  | Generator &           | Generator             |

|                                                                        |                 | Analyzer              |                           | Analyzer              |                       |

| Features                                                               |                 |                       |                           |                       |                       |

| Maximum Bit Rate                                                       | 7.5Gb/s         | 7.5Gb/s               | 12.5Gb/s                  | 12.5Gb/s              | 12.5Gb/s              |

| Flexible Pattern Generation                                            | ~               | ~                     | ~                         | ~                     | ~                     |

| BER Measurement                                                        | ~               | ~                     | ~                         | <ul> <li>✓</li> </ul> | -                     |

| Eye Diagram, Mask Testing                                              | ~               | ~                     | ~                         | <ul> <li>✓</li> </ul> | -                     |

| BER Contour, Jitter Peak, Compliance Contour                           |                 | ~                     |                           | <ul> <li>✓</li> </ul> | -                     |

| Stress Insertion for Jitter Tolerance Receiver Testing                 |                 | ~                     | ~                         |                       | <ul> <li>✓</li> </ul> |

| Ability to stress an external clock                                    |                 | <ul> <li>✓</li> </ul> | <ul> <li>✓</li> </ul>     |                       | ~                     |

| Many Subrate Clock Output Divide Ratios                                |                 | <ul> <li>✓</li> </ul> | <ul> <li>✓</li> </ul>     |                       | ~                     |

| Jitter Tolerance Templates                                             |                 | <b>v</b>              |                           | <b>v</b>              |                       |

| Options                                                                |                 |                       |                           |                       |                       |

| Option PL - Physical Layer Test Suite: BER Contour, Jitter Peak,       | Option          | <b>v</b>              | Option                    | ~                     |                       |

| Compliance Contour                                                     | Uption          | V                     | Uption                    | V                     | -                     |

| Option JTOL - Jitter Tolerance Template Testing with library of        |                 | 10-4                  |                           | A mandal and an       |                       |

| common SJ Templates and Margin Test to Failure feature                 |                 | (Software upgrad      | le option for BERTScope S | A model owners)       |                       |

| Option LDA - Live Data Analysis                                        | Option          | Option                | Option                    | Option                | -                     |

| Option ECC - Error correction coding analysis of error location        | Onting          |                       | Onting                    |                       |                       |

| data. Emulates ECC algorithms for 1-D, 2-D correctors                  | Option          | ~                     | Option                    | ~                     | -                     |

| Option MAP - Error mapping analysis of error location data. Error      | Option          | ×                     | Option                    | ~                     |                       |

| mapping visualizes errors in a 2-D map using axis dividers             | υριιση          | ~                     | υρτισπ                    | v                     | -                     |

| Option RACK - Rackmount Hardware. Kit includes all mounting            |                 |                       |                           |                       |                       |

| brackets, slides and hardware necessary to mount a BERTScope           | Option          | Option                | Option                    | Option                | Option                |

| into a standard 19" rack. Slides are adjustable for rack rails 17.5 to |                 |                       |                           |                       |                       |

| Option 3YR - Extended warranty. Adds two years to the standard         | Ontion          | Ontion                | Ontion                    | Ontion                | Ontica                |

| one-year product warranty                                              | Option          | Option                | Option                    | Option                | Option                |

| Option CAL - Calibration certificate                                   | Option          | Option                | Option                    | Option                | Option                |

| BERTScope Upgrades - BERTScope 12500 xxxx unless otherwise stated      |                 |                       |                           |                       |                       |

| 7500A to S 7500B (BERTScope 7500 A2B)                                  | Option A2B      |                       |                           |                       |                       |

| 7500A to 12500A                                                        |                 |                       |                           |                       |                       |

| S 7500B to S 12500B                                                    | Option UP       |                       |                           |                       |                       |

| 7500A to S 12500B                                                      | Option UPS      |                       |                           |                       |                       |

| S 7500A to S 12500B                                                    | 59000 01 0      | Option SUPS           |                           |                       |                       |

| 12500A to \$ 12500B                                                    |                 | 0,00,00,0             | Option A2B                |                       |                       |

| S 12500A to S 12500B                                                   |                 |                       | 0,000,0020                | Option SA2B           |                       |

| SPG to S 12500B                                                        |                 |                       |                           | 000000000             | Option PG2B           |

🖌 - Standard feature

– - Not Available

Option - Available by adding the listed option

For more information on this and other products:

- BERTScope<sup>™</sup> and BERTScope<sup>™</sup> S Signal Integrity Analyzers Technical Specifications, SR-DS014

- BERTScope<sup>™</sup> SPG Product Brief, SR-DS019

- BERTScope™ Differential ISI Board Product Brief, SR-DS018

- BERTScope™ CR Clock Recovery Instrument Product Brief, SR-DS016

Application information:

- Stressed Eye Know what you are testing with, January 2006

- Constructing a 10 GbE Optical Fibre Channel Stressed Eye, January 2006

- Constructing a 4x FC Optical Stressed Eye, January 2006

- Testing the High Speed Electrical Specifications of an

- XFP Transceiver, July 2006 • Evaluating Stress Components Using BER-Based Jitter

- Evaluating Stress components Using BER-Based Jitter Measurements, September 2005

3475-D Edison Way Menlo Park, CA 94025 U.S.A. Voice 650 364-1853 Fax 650 364-5716 info@synthesysresearch.com www.synthesysresearch.com BERTScope is a trademark, and BitAlyzer and Error Location Analysis are registered trademarks of SyntheSys Research, Incorporated. U.S. and International patents granted and pending. Windows is a registered trademark of Microsoft Corporation.

Copyright © 2005-2006 SyntheSys Research, Inc.. All rights reserved. Printed in USA. Specifications subject to change.

SR-DS014 180CT06